| Mar 20, 2026 |

Researchers developed a dual-modulated vertically stacked transistor that eliminates current leakage at nanoscale channel lengths, advancing low-power 3D chip integration.

(Nanowerk News) Researchers have developed a vertically stacked transistor with a dual-modulation architecture that eliminates current leakage at nanoscale channel lengths. The team, led by Professor Jae Eun Jang and Dr. Goeun Pyo at DGIST’s Department of Electrical Engineering and Computer Science, demonstrated stable device operation in two-dimensional channel structures without the costly alignment processes typically required for such designs.

|

|

The results, published in Advanced Science (“Dual‐Modulated Vertically Stacked Transistors With Fully Laminated Plate‐Type Architecture Featuring Nanoscale Channel Length”), offer a practical path toward highly integrated, low-power 3D semiconductors.

|

Key Findings

- A sandwich-like transistor structure with upper and lower gates controlling the channel through independent mechanisms suppresses leakage current to 10⁻¹² amperes in the off state.

- Microscopic openings in the lower electrode allow electric signals to reach deeper into the channel, while a graphene upper electrode provides precise current control.

- The fabrication process avoids high-temperature steps and ultra-precise alignment, making it compatible with large-area and multilayer production.

|

|

As chipmakers push to fit more transistors into shrinking footprints, vertical stacking of current-carrying channels offers a way to increase device density without expanding chip area. Instead of spreading circuits across a flat plane, vertically stacked transistors layer channels on top of one another. But shrinking the channel length in these vertical devices creates a persistent problem: the gate electrode, which switches the transistor on and off, cannot deliver its electric signal uniformly throughout the channel interior. The result is unwanted current leakage and erratic switching behavior.

|

|

The DGIST team tackled this by placing two gates on opposite sides of the channel, each operating through a different control mechanism. In this sandwich configuration, the lower electrode features microscopic openings that allow the gate field to penetrate more deeply into the channel material.

|

|

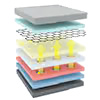

| Transistor structure and operation principles of the dual-modulated vertically stacked transistor. The center diagram shows the layered architecture, from the PE-Gate at the bottom through the patterned electrode source with micro-hole blocking layer, channel, graphene drain, and Gr-Gate on top. Left panels compare a conventional planar transistor with the vertically stacked design. Right panels illustrate how the two gates modulate current flow: the graphene gate adjusts the Fermi level at the channel interface, while the patterned electrode gate controls field penetration through the micro-hole openings. (Image: DGIST) (click on image to enlarge)

|

|

The upper electrode is made of graphene, a single-atom-thick carbon sheet whose electrical properties allow finer modulation of current flow. A dedicated blocking layer was added in regions where leakage pathways would otherwise form, eliminating unnecessary power loss.

|

|

The resulting device achieves a conduction layer only nanometers thick. When switched off, the transistor limits stray current to roughly one trillionth of an ampere (10⁻¹² A), giving it a sharp distinction between its on and off states. It delivers adequate output current at low operating voltages and holds up under conditions that typically degrade performance, including light exposure and extended operation.

|

|

One of the design’s practical advantages is its compatibility with existing fabrication workflows. Because the process requires neither extreme temperatures nor sub-nanometer alignment precision, it can be scaled to large wafer areas and extended to multilayer stacks without prohibitive cost increases. That scalability positions the technology for use in highly integrated 3D semiconductors, low-power logic devices, memory technologies, and flexible electronics.

|

|

“This research presents a new dual-gate design strategy that enables stable operation even in nanoscale channels,” stated Professor Jae Eun Jang of the Department of Electrical Engineering and Computer Science at DGIST. “By overcoming the fundamental limitations of conventional vertical transistors, the technology is expected to serve as an important solution for accelerating the era of next-generation low-power, highly integrated 3D semiconductors.”

|

|

The ability to suppress leakage at such small scales while maintaining clean on/off switching addresses one of the central bottlenecks in 3D chip integration. If the approach proves transferable to industrial production lines, it could shorten the path to deploying vertically stacked architectures across the application areas the team identified.

|