| Mar 16, 2026 |

Researchers developed a dual-modulated vertical transistor that suppresses leakage at nanoscale channels and supports scalable 3D semiconductor integration.

(Nanowerk News) Researchers at the Daegu Gyeongbuk Institute of Science and Technology (DGIST) in South Korea have developed a vertically stacked transistor that operates reliably at nanoscale channel dimensions without current leakage. The device, described as a “dual-modulated vertically stacked transistor,” uses two independently controlled gates positioned above and below the channel, paired with a graphene electrode and a dedicated leakage-blocking layer.

|

|

Published in Advanced Science (“Dual‐Modulated Vertically Stacked Transistors With Fully Laminated Plate‐Type Architecture Featuring Nanoscale Channel Length”), the work demonstrates a fabrication approach that avoids expensive ultra-precision alignment processes, opening a path toward large-area manufacturing and multilayer 3D semiconductor stacking.

|

Key Findings

- A sandwich-structured vertical transistor with dual top and bottom gates suppressed off-state leakage current to 10⁻¹² amperes while maintaining clear distinction between on and off states.

- Microscopic openings in the lower electrode combined with a graphene upper electrode allowed gate signals to reach the full depth of the channel interior.

- The entire fabrication process runs at low temperatures and requires no high-cost precision alignment, supporting both large-area production and repeated vertical stacking.

|

|

The semiconductor industry is under growing pressure to fit more devices into limited space, but conventional scaling methods are approaching physical limits. Vertically stacked transistors, in which current-carrying channels are layered on top of one another, offer higher density without expanding the chip footprint.

Yet a core weakness of this architecture persists: the electrode structure prevents gate electric signals from being delivered uniformly into the channel interior. As channel length shrinks, that uneven field distribution produces current leakage and erratic switching.

|

|

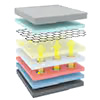

| Transistor structure and operation principles of the dual-modulated vertically stacked transistor. The center diagram shows the layered architecture, from the PE-Gate at the bottom through the patterned electrode source with micro-hole blocking layer, channel, graphene drain, and Gr-Gate on top. Left panels compare a conventional planar transistor with the vertically stacked design. Right panels illustrate how the two gates modulate current flow: the graphene gate adjusts the Fermi level at the channel interface, while the patterned electrode gate controls field penetration through the micro-hole openings. (Image: DGIST) (click on image to enlarge)

|

|

The DGIST team, led by Professor Jae Eun Jang and Dr. Goeun Pyo from the Department of Electrical Engineering and Computer Science, resolved this by arranging upper and lower electrodes to face each other across the channel in a sandwich-like configuration. Each gate governs the channel through a distinct mechanism. The lower electrode contains microscopic openings that let the gate electric field penetrate deeper into the channel, rather than being screened by a solid metal surface. The upper electrode is made of graphene, a single-atom-thick carbon material whose electrical properties shift in response to an applied field, allowing finer regulation of current flow at the channel boundary.

|

|

In regions where the electrodes overlap vertically, the team inserted a blocking layer that eliminates the pathways through which unnecessary current would otherwise escape. This targeted intervention addresses one of the most common sources of power loss in vertical transistor designs, where overlap between electrodes creates routes for leakage even when the device is nominally switched off.

|

|

Together, these elements produced a conducting layer in an extremely thin planar form at the nanometer scale, far thinner than the diameter of a human hair. Off-state leakage current was held to just 10⁻¹² amperes, well below the threshold needed to separate on and off states cleanly. The transistor also delivered adequate output current at low voltages and held steady under conditions that typically degrade thin-film devices, including exposure to light and extended periods of continuous operation.

|

|

“This research presents a new dual-gate design strategy that enables stable operation even in nanoscale channels,” stated Professor Jae Eun Jang. “By overcoming the fundamental limitations of conventional vertical transistors, the technology is expected to serve as an important solution for accelerating the era of next-generation low-power, highly integrated 3D semiconductors.”

|

|

A notable practical feature of the approach is that it sidesteps several manufacturing bottlenecks. The process operates entirely at low temperatures, so each new layer can be deposited without thermally damaging the ones already in place. And because the design does not depend on high-precision alignment equipment, it is well suited for scaling to large-area substrates and for building structures with many stacked transistor layers.

|

|

The researchers identified several areas where the technology could be applied: highly integrated 3D semiconductor circuits, low-power logic devices, memory systems, and flexible electronics built on non-rigid substrates. The ability to combine nanoscale channel control with a straightforward, low-temperature stacking process addresses a gap that has kept vertical transistor architectures from moving beyond laboratory demonstrations toward viable manufacturing.

|